SYNOPSYS (SNPS)

Leader in Electronic Design Automation ( EDA)

Synopsys (SNPS)

Synopsys (SNPS) is an American Electronic Design Automation (EDA) company headquartered in California.

SNPS was founded in 1986 by Aart de Geus (Current Chairman and CEO), David Gregory, and Bill Krieger.

It was established to develop and market logic synthesis technology developed by the team at General Electric's Advanced Computer-Aided Engineering Group.

It changed its name to Synopsys in 1987 and had its IPO in February 1992.

EDA is a software industry that provides computer-aided design (CAD) tools for the design, analysis, and verification of Chips and Electronic Systems.

Products are used by semiconductor and technology companies .

In 2023, SNPS has approximately 19,000 employees. It has offices in more than 20 countries.

SNPS’s employees are highly skilled engineers, scientists, and business professionals who are dedicated to developing innovative solutions that help customers accelerate electronics innovation.

SNPS’s products and services are difficult for the non-expert (like me) to understand.

In contrast, there is nothing ambiguous about SNPS’s business and financial performance which has clearly been very good.

Semiconductors / Silicon Chips

Semiconductors or Silicon Chips are at the heart of the technological transformation in the global economy. Semiconductors are everywhere: in computers, cars, home appliances, medical equipment, electronic devices etc.

Semiconductor companies will sell US$800 billion worth of chips this year.

Steve Blank of Stanford University has written a helpful article on the semiconductor ecosystem which can be accessed here

Blank’s scheme is summarised below:

Seven Segments of the Semiconductor industry

Chip IP Cores: Selling Chip Designs.

ARM Computer, Synopsys (SNPS), Cadence Design Systems (CDNS)

EDA Tools: Selling Design Tools.

Synopsys (SNPS), Cadence Design Systems (CDNS), Siemens

Specialised Materials: Selling materials needed in Chip Manufacture such as gases and chemicals.

Air Liquide, Linde, Dow Chemical

Wafer Equipment Producers: Selling Capital Equipment to Chip Manufacturers.

ASML, Applied Materials (AMAT), KLA (KLAC), Lam Research (LCRX)

Fabless Chip Companies: Chip designers who do not manufacturer

Qualcomm (QCOM), Broadcom (AVGO), Nvidia (NVDA), Apple (AAPL), Amazon (AMZN), Tesla (TSLA), Meta Platforms (Meta), etc

Integrated Device Managers (IDMs) : Designers and Manufacturers of Memory, logic and analogue chips.

Analog Devices (ADI), SK Hynix, Micron (MU) and Texas Instruments (TXN), Intel (INTC), AMD.

Chip Foundries: Contract manufacturers of Chips.

Taiwan Semiconductor (TSMC), Samsung, Intel (INTC) and GlobalFoundries (GFS)

SNPS’s business is in the top two segments above. It is a major player in EDA Tools and IP Cores along with CDNS. Much of what is said about SNPS also applies to CDNS.

Before we discuss SNPS, we will briefly talk about Moore’s Law.

Moore's law

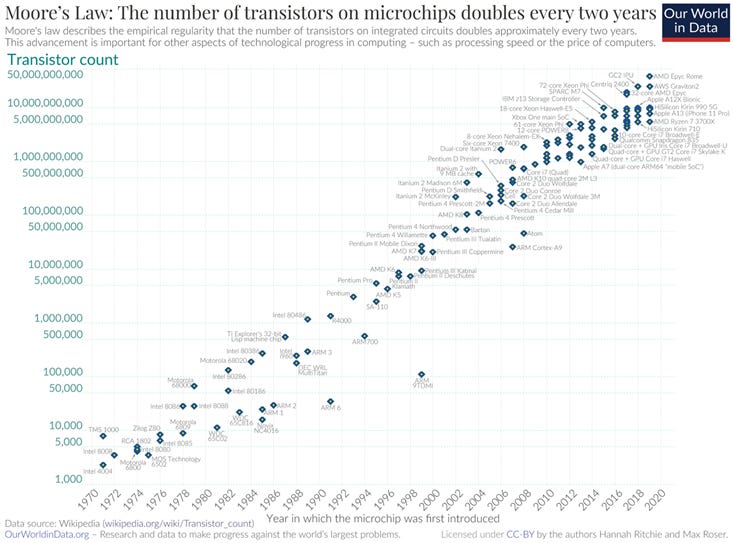

Moore's law is named after Gordon Moore of Intel. It is an observation, made in 1967, that the number of transistors in an integrated circuit (IC) doubles approximately every two years. It implied that computer chip performance would roughly double every two years (with no increase in power consumption). Moore's Law predicted that transistor count would double every 2 years due to shrinking transistor dimensions and other improvements.

The increase in the transistor count in a microchip has been exponential in the last 50-60 years (50mn+ times). An improvement on this scale is difficult to comprehend. Michio Kaku, the physicist and popular author expressed the impact of Moore’s law put it, “Today, your cell phone has more computer power than all of NASA back in 1969, when it placed two astronauts on the moon.” Of course, this is a headline grabbing simplification. Your smartphone probably could not land a man on the moon. A qualifying argument is made here.

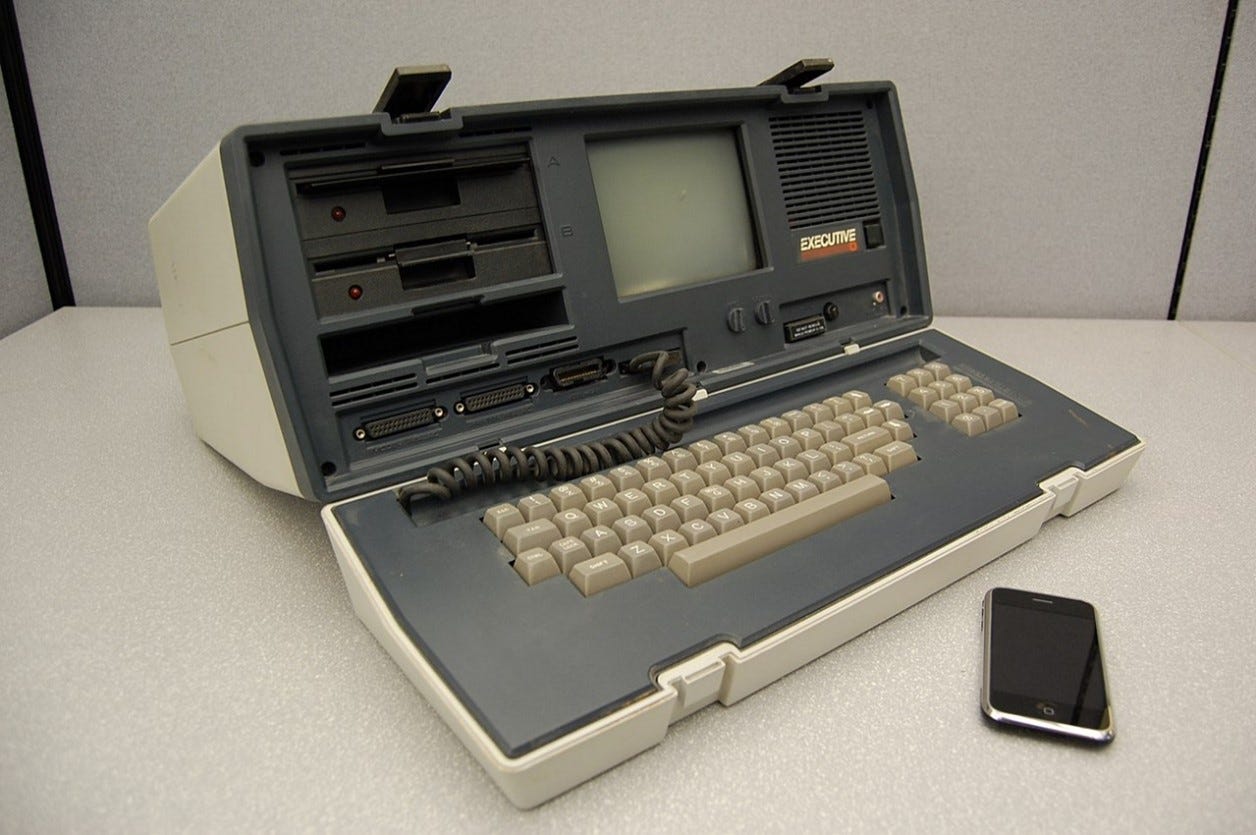

Source: Casey Fleser @Flick.com

The photograph above shows an Osborne Executive computer, from 1982 (with a Zilog Z80 4 MHz CPU) and a 2007 Apple iPhone (with a 412 MHz ARM 11 CPU). The former has 100X the weight, almost 500x the volume, approximately 10x the inflation adjusted cost, and 1/103rd the clock frequency of the 2007 Smartphone. Todays most advanced smartphone chip (Apple A16) is about 10x more powerful than the one in the 2007 iPhone.

As a prediction, Moore’s Law has been remarkably accurate. It has been a driving force in the semiconductor industry for over 50 years and has enabled the provision of increasingly powerful and affordable computers, smartphones, and other electronic devices.

Here are some of the key factors that have enabled Moore's law to law to continue for so long:

New design techniques: The semiconductor industry has developed new design techniques that allow more transistors to be packed into a given space.

Improvements in manufacturing processes: The industry has made significant improvements in its manufacturing processes over the years.

New materials: The industry has developed new materials better suited for use in transistors.

These factors have combined to enable the creation of transistors that are smaller, faster, and more efficient. The first factor is the most relevant to SNPS.

We also need to briefly discuss nanometers (nm) as a numerical measure of progress in chip design. It refers to the size of the smallest features on the chip. It determines how many transistors can be packed onto the chip, which in turn affects the chip's performance and power consumption.

A 10-nanometer (10nm) chip can fit about 100 million transistors, while a 7-nanometer (7nm) chip can fit about 1 billion transistors. This means that the 7nm chip can perform calculations much faster than the 10nm chip and will also use less power. Moore’s Law has allowed integrated circuits to become smaller, faster, and more powerful over time.

However, there are physical constraints as to how small the features on a chip can be made. The Laws of Physics limit how many more transistors can be packed onto a piece of Silicon. As the nm count gets lower, it becomes much more difficult and expensive to manufacture leading edge chips reliably. Twenty years ago, there were 17 companies which could manufacture leading edge chips but today only two companies (Taiwan Semiconductor and Samsung) are able to do so. A leading-edge chip fab (factory for building chips) has a minimum capital cost of US$ 10bn.

The physical challenges of making transistors smaller and smaller are becoming increasingly difficult to overcome. This is one (of many) reason that designers and manufacturers of new semiconductors face much greater challenges and obstacles to further progress.

Synopsys

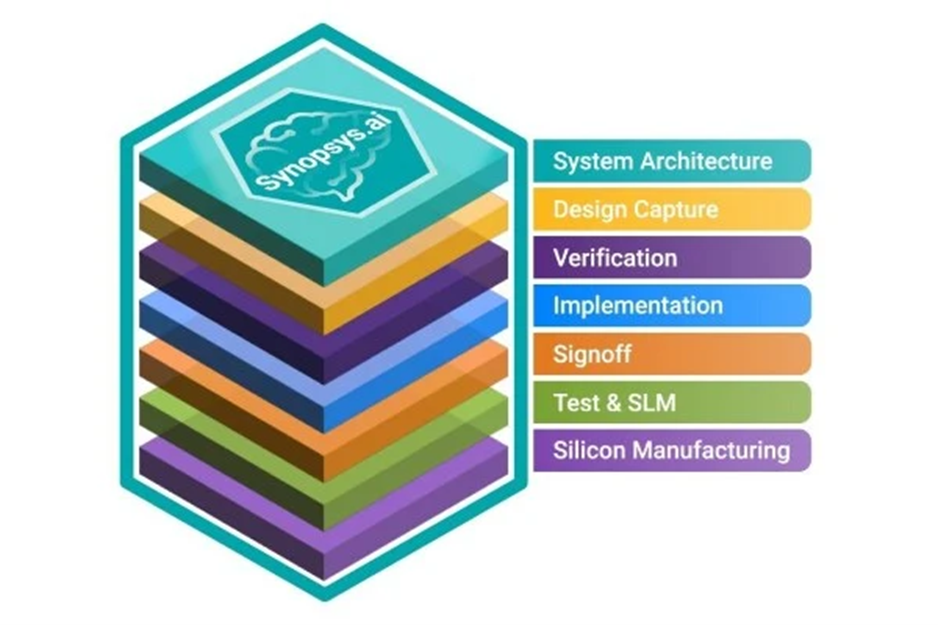

The products offered by Synopsys are as follows:

Core EDA

IP Systems

Software Integrity.

Manufacturing Solutions, and

Professional Services.

1. Core EDA

Core EDA provides tools and services for the design and verification of integrated circuits (IC) and IC Systems. EDA software allows engineers to plan and test integrated circuits designs.

2. IP Systems

This segment provides IP blocks for use in IC designs. These are pre-designed circuits that engineers use as components of larger chip designs.

3. Software Integrity

This segment provides software and hardware used to develop the electronic systems that incorporate chips and the software that runs on them.

4. Manufacturing Solutions and Professional Services

This segment provides technical services to support its solutions and help its customers develop chips and electronic systems. It is also a provider of software tools that developers use to develop software code in a range of industries, including electronics, financial services, energy, and industrials.

Since its inception the SNPS has grown strongly in line with the global semiconductor industry.

It is the market leader in EDA where it has 35 years of experience, and which generates 65% of SNPSs revenues.

It is the no2 in Design IP where it has 25 years of experience and generates 25% of its revenues.

SNPS is a market leader in software integrity where it has 9 years of experience, and it generates 10% of its revenues.

EDA

SNPS management estimates this market is currently worth US$ 9.9bn and growth is driven by R&D budgets rather than prevailing demand for semiconductors. A cyclical downturn does not hit the demand for SNPS’s EDA products. During economic downturns, the industry invests strongly in chip design so that when the downturn fades away, they have differentiation in product as the worst outcome is to miss an upturn because that's where most of the money is made. A secular, sustained decline in the industry would hit demand but that has not happened in the last 40 years. All leading semiconductor companies use SNPS’s technology. The company offers state of the art design and verification solutions coupled with, what it claims, to be unmatched global support.

Design IP

Company offers reusable building blocks that are used for Chip Design. The company estimates that the market size is currently US$ 6.7bn and growth will be driven by the fact that customers are moving towards outsourcing more and more complex IP. Demand is being driven by rapidly increasing complexity due to developments in AI, Automotive (assisted driving / the connected car), Cloud (huge migration to the Cloud) and the Internet of Things (Smart homes factories and ubiquitous connected devices).

Synopsys' products and services are used by semiconductor companies of all sizes, from small startups to large multinational corporations. The company's customers include Apple, Samsung, Intel, Qualcomm, Ansys and distributors/re-sellers such as Arrow Electronics. No one customer accounts for more than 3.5% of revenues.

The limits to Moore’s Law and rapid technological change makes life for chip designers very difficult. They must develop much more complicated products much more quickly. They need more of the products and services supplied by SNPS.

The design process for chips

The design process for an IC or silicon chip typically begins with a specification. The specification defines the functionality and performance requirements. Once the specification is complete, the design process can begin.

The design process is divided into 2 main phases:

Front-end design: This phase includes the design of the IC's logic and architecture.

Back-end design: This phase includes the design of the IC's physical layout and the verification of the design.

Synopsys provides tools and services for both front-end and back-end design phases.

Synopsys is also investing in new technologies, such as artificial intelligence (AI) and machine learning (ML). These technologies have the potential to revolutionize the design process and make it more efficient and effective.

The market is divided among three vendors: Synopsys (SNPS), Cadence Design Systems (CDNS) and Siemens (who entered this market through its acquisition of Mentor Graphics) in that order.

This provides a very stable but fierce competitive environment with vendors constantly looking to gain and defend market share through incremental product innovation.

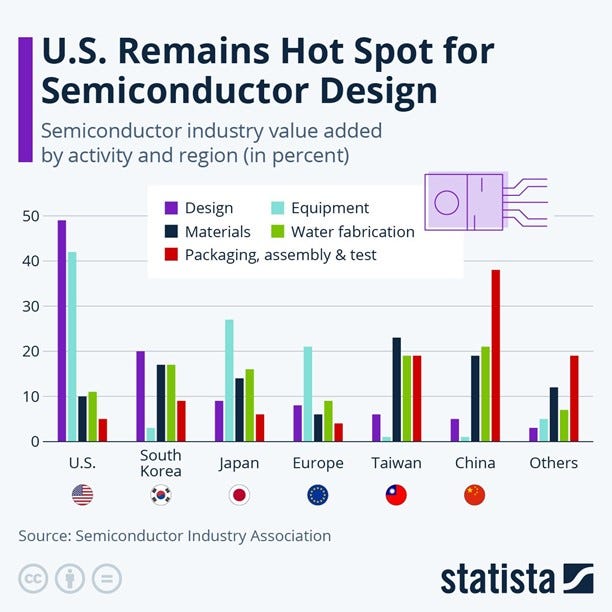

The Revenue shares (%) by geography are as follows:

USA 48.1%

China 11.4%

Korea 10.6%

Europe 26.2%

ROW 3%

This roughly reflects where Chip design activity is located. This is the purple bar in the chart below:

Rapid pace of technological innovation

The pace of innovation is moving at a rate rarely seen before. Current innovation trends are being driven aggressively by a number of factors including:

1. Cloud: The trend for owned on-premises infrastructure to be replaced by always available, always connected, rented by the hour, Cloud infrastructure.

2. EV: The rise of Electric Vehicles and assisted/automated driving.

3. IOT: The rise of the Internet of Things (IOT) which require all devices to be smart and connected.

4. AI/ML: The rise of Machine Learning (ML) and Artificial Intelligence (AI).

Leading-edge manufacturers from big names like Apple and Tesla to new start-ups, are now beginning to realize great gains in silicon and system-level development as they seek to escape the confines of Moore’s Law.

Intelligent Co-Optimization of Software and Hardware Leads to Rapid Innovation

In the past that hardware engineers would work in silos and would push software engineering teams to complete full solutions. Now, however, the best practice is based on a co-development model. Advanced system designs can only be fully optimized by taking a holistic approach, and bringing software development and use-case workloads together with hardware chip-level design. This approach can lead to advances that would not be possible if the workflow was reliant on just semiconductor process and other hardware-focused advancements.

Consider Apple’s internal silicon development effort with its M1 and M2 series of processors for its MacBook and Mac Mini portfolio. We noted in our report on Apple that it replaced Intel Chips with the in-house designed M1 and M2 processors. As a result, they achieved much faster performance and much higher battery life for desktops and laptops.

By engineering its own tightly-coupled, highly advanced solutions – with its software and application workloads considered during the design of the hardware — Apple demonstrated it can do more with less, with arguably, some of the best performance-per-watt metrics in the PC industry.

Likewise, Tesla has realised realized if it is to achieve its goal of full level 4 and 5 self-driving autonomy in cars, it will have to engineer its own custom silicon engines and systems. The company has been a pioneer in FSD (Full Self-Driving) chip technology.

Apple and Tesla have huge resources and big budgets for their in-house chips and technology. However, SNPS (and CDNS) are developing and supplying new tools, bolstered by advancements in AI, which will allow small companies to design their own chips, or at least develop more optimized solutions which are powerful and efficient relative to general purpose chips and off-the-shelf solutions.

Synopsys Cloud

In the last two years, SNPs has been offering its products on the Cloud. The customer gets access to the products on their desktops/ laptop computers at the edge with support from SNPSs but on infrastructure provided and maintained by the Cloud Hyperscalers such as Amazon AWS or Microsoft Azure. All major Cloud Hyperscalers are SNPS’s partners.

The offering dubbed “Synopsys Cloud” makes its cutting-edge design and verification tools available to a diverse spectrum of potential customers.

Synopsys AI

The company has responded to development in AI to boost their product offering.

Its offerings here are dubbed Design space Optimisation.ai (DSO), Verification Space Optmisation.ai (VSO) and Testing Space Optimisation (TSO.)

The company claims they have an industry-leading AI-driven design platform, Synopsys.ai (See below)

DSo.ai employs machine learning to drive dramatically faster place and route processes for design engineers to deliver better, faster, and cheaper semiconductors. There is a critical step in the semiconductor design process, known as floor planning, where chip designs are mapped to Silicon. The iterative nature of the process, targeted at optimizing for silicon area, power and performance goals, is a natural task for machine learning and can dramatically improve time to market and engineering man-hours, freeing up engineers to focus on new innovations.

AI is also advancing the verification and validation process of chips, where the goal is to wring out anomalies and application marginalities before chips are sent to mass production and deployment.

According to the company “Validation and verification are great opportunities for machine learning, where the AI can help not only time to market, but also expand the test coverage area, which can be especially critical for general purpose silicon that needs broader confidence in a wider range of applications.”

The chart below the various products and services that SNPS offers to try and bridge the gap between what the market currently demands and what is possible under the current limitations of Moore’s Law.

SNPS’s Financial Profile and Performance

SNPS products and services are difficult for the non-expert (like me) to understand.

In contrast, there is nothing ambiguous about SNPS business and financial performance which has clearly been very good.

Revenues were US$ 40mn at the time of the IPO in 1992. They were US$ 1.5bn in 2012 and US$ 5bn in 2022. Over the last 10 years, Net Income has grown from US$ 182mn to US$ 984mn (5.4x).

In the last decade, investors have seen a 10X return. Over two decades the annual CAGR return has been 45%.

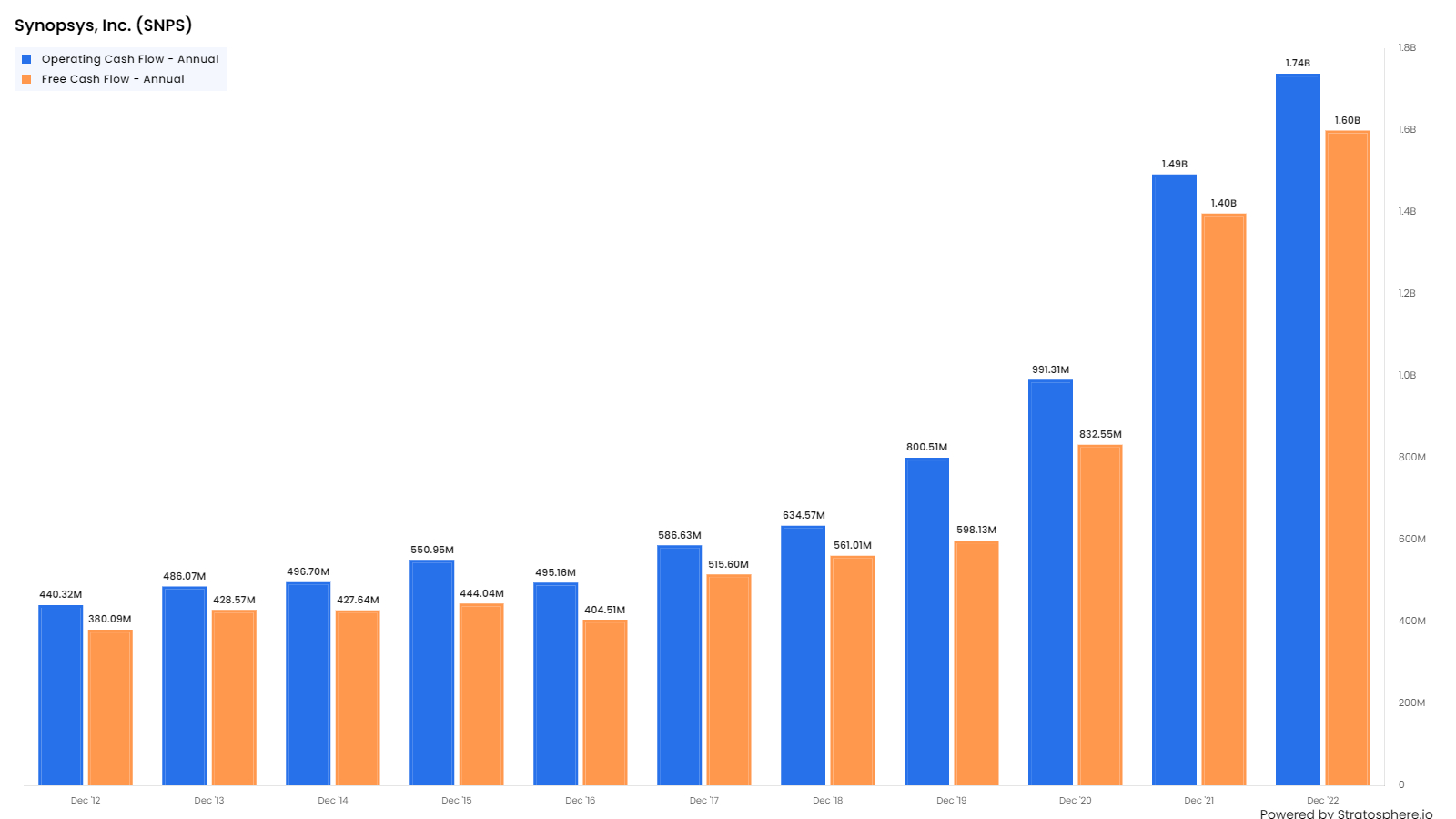

The growth in profits in the last decade has been accompanied by ~ 4X growth in both Operating and Free Cash Flow.

Key: Orange line - Total Assets. Blue Bars- Goodwill and Intangible Assets

The balance sheet has doubled in the last 8 years ( to US$ 9.8bn) and goodwill /intangibles have also grown reflecting the impact of several acquisitions. The latter have consistently been around 40%-50% of Total Assets. The company has no debt and currently has net cash of around US$ 1.6bn. Therefore, the balance sheet is strong.

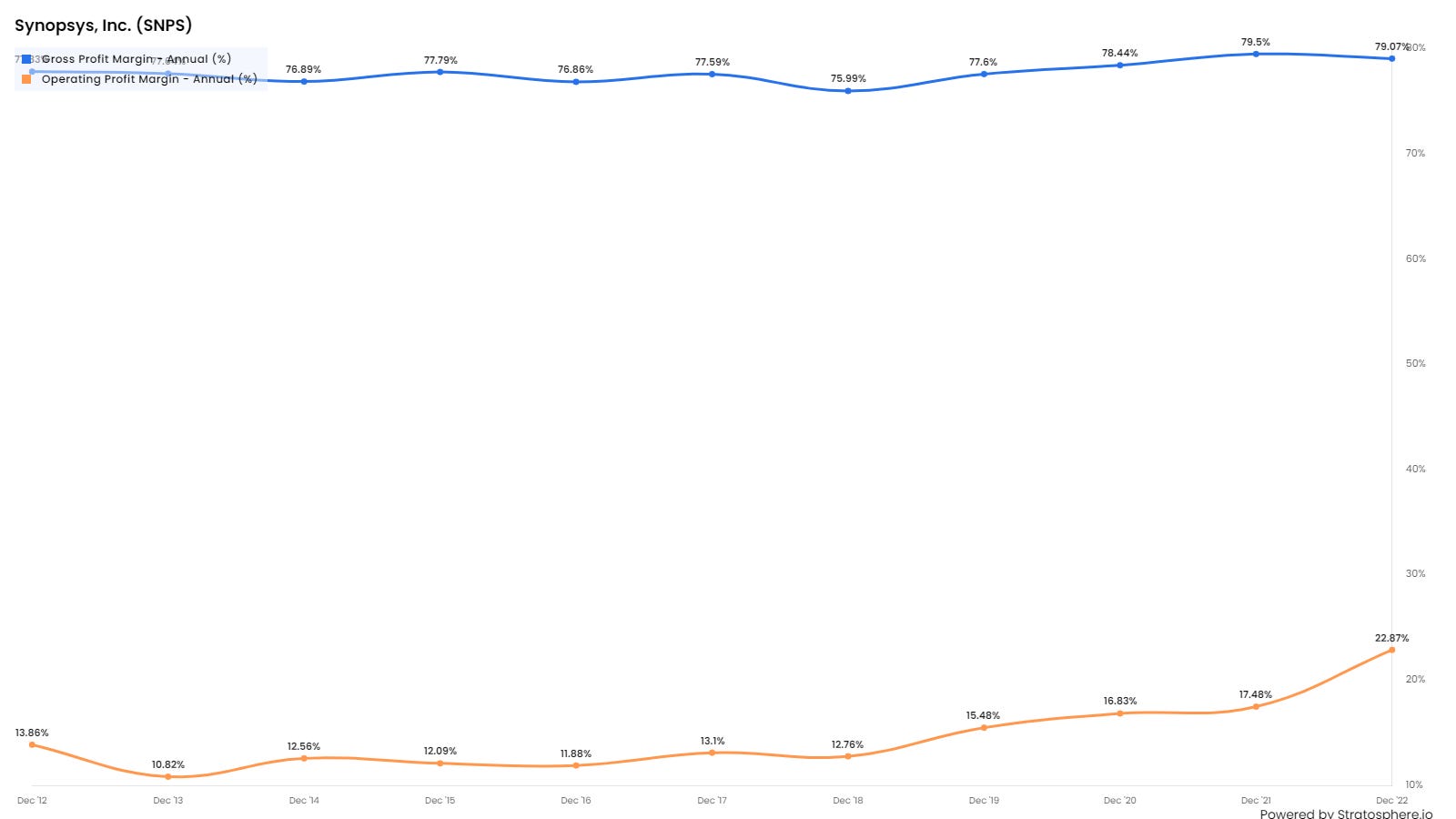

In the last year, gross margins have been stable at about 78% while Operating margins have risen from 12.6% to 18%. The difference between is explained by R&D (34% of revenue) and SSGA (23%). R&D Expense has been a high 30% to 35% of Revenue in the last 8 years.

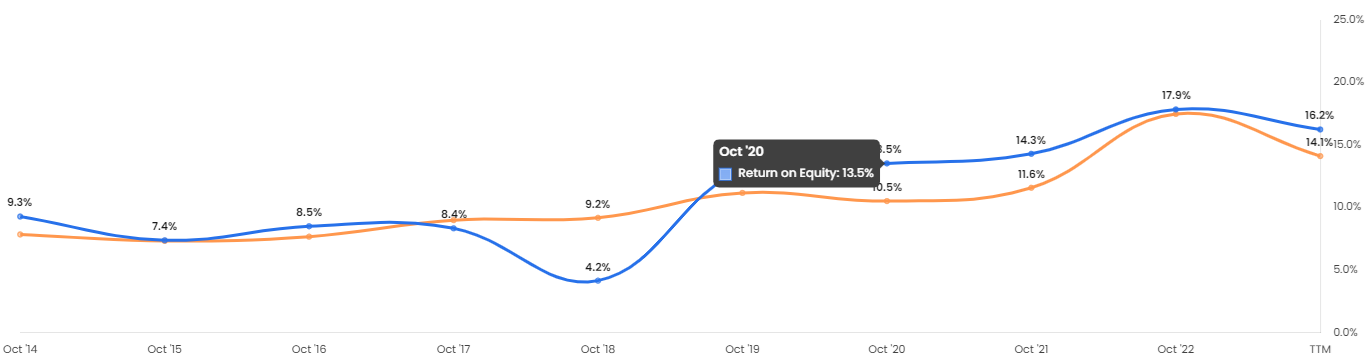

Key: Blue Line–Return on Equity(ROE). Orange Line–Return on Invested Capital (ROIC)

ROE has risen from 9.33% in 2014 to 16.2% currently. ROIC has risen from 8.7% in 2014 to 14.1% currently. These are not as high as some technology companies we have looked such as Microsoft, Apple, Meta etc but higher than Ansys.

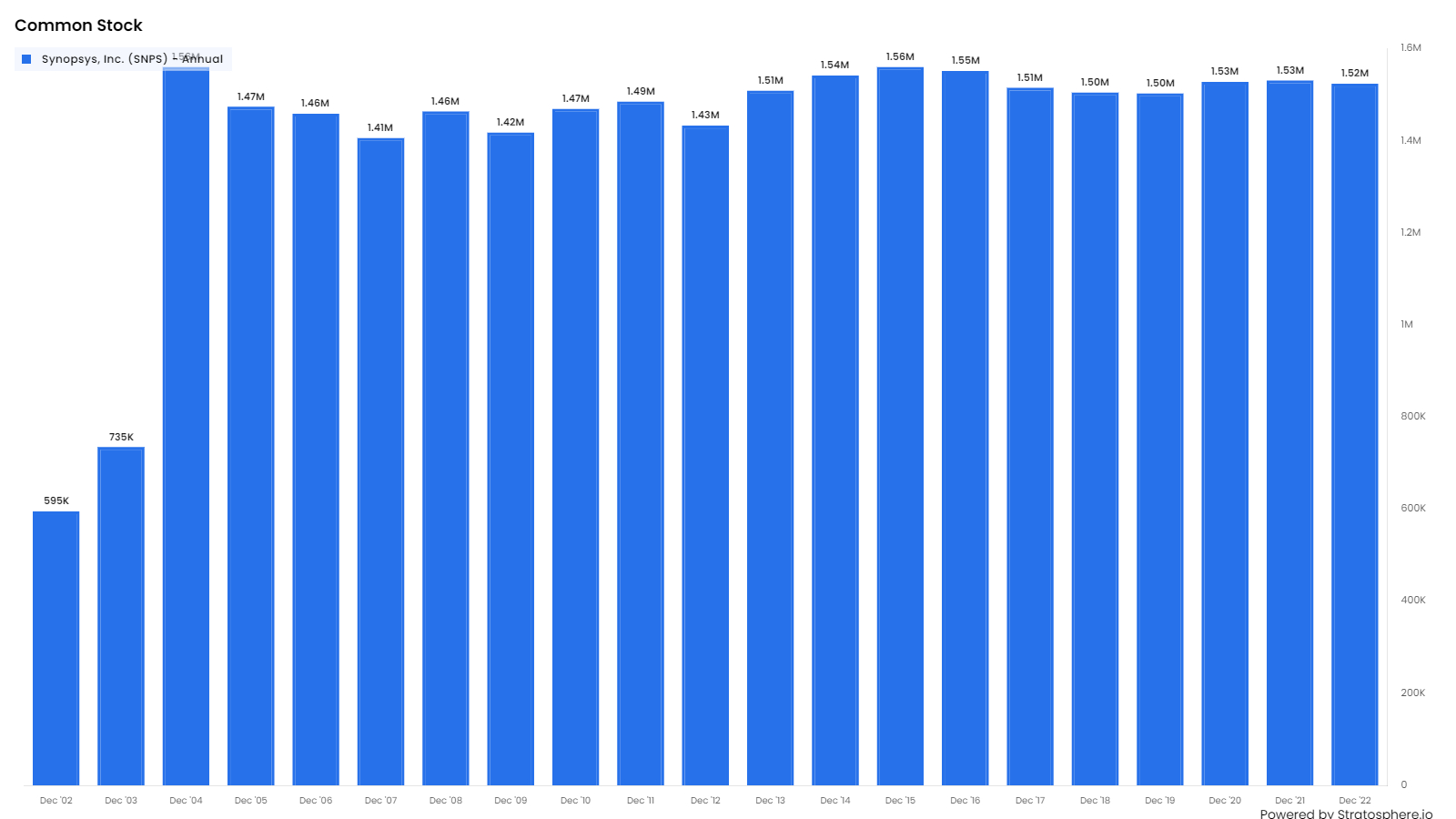

The company has been consistently buying back stock in the last twenty years as shown in the chart above. It is shown as negative as stock buybacks are a cash outflow. However, the number of shares outstanding at 155mn has not fallen. This suggests share buybacks are merely offset the shares issued to employees as stock-based compensation. This is just a transfer of money from shareholders to employees. The former get no benefit from the share repurchase programme.

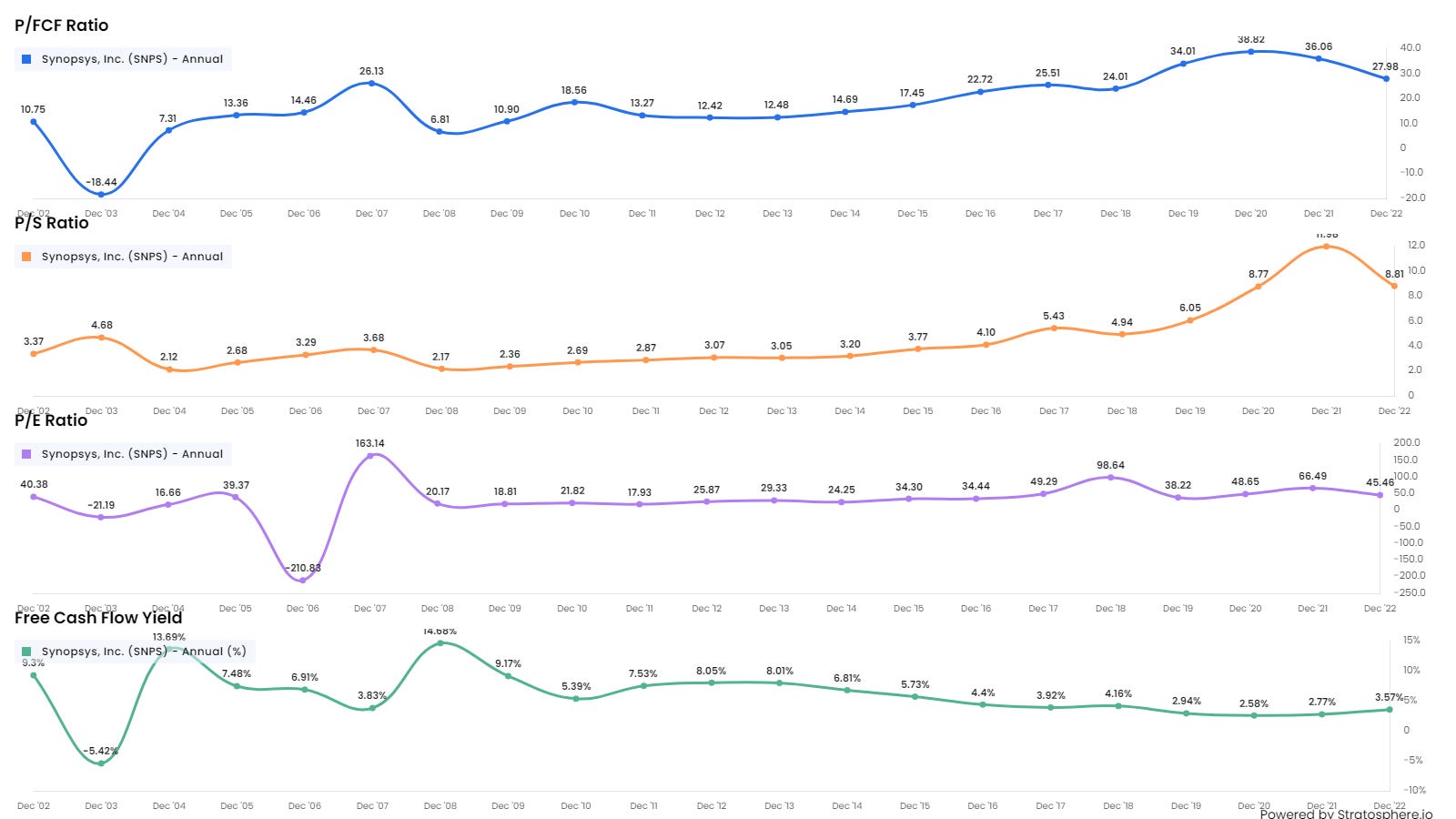

Valuation Ratios: The quick summary valuation ratios for SNPS are shown below:

The summary valuations investors normally look at are quite high for Synopsys.

The historic P/E Ratio is 45.6 times. The forward P/E Ratio is ~34 times. The historic Price /FCF ratio is 28 times. The FCF yield is 3.6% which is more reasonable but below current short-term US interest rates.

Excerpts from the Results Press release and Conference Call on 17th May 2023

“Exceptional execution across the company drove strong quarterly financial performance,” said Shelagh Glaser, CFO of Synopsys. “We have a resilient business model uncommon in software companies and remain confident in our business. We are raising our full year guidance and expect revenue growth of 14-15%, non-GAAP operating margin accretion of 150 basis points to 34.5%, and non-GAAP earnings per share growth of 21-22%.”

“There's an additional substantial driver. And you've seen it with all the excitement (about AI) , I would say, 5% hype and 95%, absolutely great understanding of the impact of what this will have on the world, where every vertical market is now committed to Smart Everything.”

“The race is on for more chips, faster chips and most importantly, chips where you can get high compute at low power. And so, this plays into the core competencies that Synopsys has. And because simultaneously, there is a shortage of top designers, the productivity enhancements that we can bring about with our own AI have a material impact on that.”

“AI is absolutely prominent in many transactions because either people have already very good experience in just racing to implement it in many more chips or use it on many more chips or they have heard from others and are racing to now look at how they can use it. At the same time, I would say that there's no alignment in big renewals across the industry. They happen whenever they happen for each one of the individual companies.”

“The semiconductor design companies that have this nonstop pressure from their customers, give me way more compute for less power and maybe roughly the same cost.”

“So in general, when you have a new field (AI/ML) that gets a lot of attention, you also get a lot of new innovation and new investments. And so I foresee that we will continue to see that moving forward at a pretty rapid clip because the demand is so high. Now underneath all of this, there are some very challenging problems. And so, while the results that we've seen are truly exciting, figuring out some of the software solutions to make sure that the results are actually truthful, that you can actually protect the intellectual property.”

Summary

Synopsys is a well-established company which has grown strongly for over 30 years by serving its customers in the high growth semi-conductor industry.

It is one of two leading companies in EDA – an industry that provides computer-aided design (CAD) tools for the design, analysis, and verification of Silicon Chips and Chip-based electronic systems.

The Company has consistently grown revenues, profits, operating cash-flows, and Free Cash Flows over decades. It has a strong balance sheet with net cash of US$ 1.6bn

It has a diverse set of customers in its targeted segment and as maintained leadership by developing products which can be used in the Cloud, and which incorporate the latest advances in AI.

Long-term investors have made a return of 45% CAGR over two decades-and 90% CAGR in the last decade- a phenomenal result.

The company looks well placed to grow strongly in the next few years as accelerating technological change (AI, IOT and Cloud) drive demand. Along with CDNS, it is a dominant player in this industry.

However, to maintain their technological leadership position, the company had to spend a substantial portion of revenue (30% to 35%) on R&D and on a regular series of acquisitions.

This means the operating margin at ~18%-19% and ROE at ~16% are less than many other tech companies.

This spending reduces Free Cash Flow. We usually prefer companies that generate a lot of Free Cash Flow which can then be used to either acquire new companies, reduce leverage, or buy back stock.

Although the company has been an active buyer of its own stock, it has not benefited shareholders, as it has just offset the dilutive impact of stock-based compensation. The number of share outstanding has been constant for a decade.

Concluding Remarks

Synopsys is an interesting company with a string position in a high growth industry.

The stock has had as good run recently and a forward P/E Ratio of ~35 times feels expensive /fully valued for a company with an ROE/ROIC of about 18%.

We ran a simple DCF model - These of course should come with a warning as the final result is very sensitive to the input. A small change in the latter can lead to a very small change in the former.

Our assumptions included:

Revenue growth slowing from 17% growth to 15% over five years.

Weighted Average Cost of Capital (WACC) at 8.6% (arguably too low but inflation could quickly fall below 3% in next few months)

The 5-year DCF give the following value ranges for a range of values for the long-term growth of the company.

Medium to Long-term Growth Assumption (%) /Estimate Fair Value of the stock (US$) from DCF Model

4% - US$ 200

5% - US$ 244

6% - US$ 324

7% - US$ 500

In this case, Medium to Long-term means Year 6 onwards.

This compares with the current stock price of ~ US$ 400.

For what it is worth (and it may not be worth very much), this DCF analysis suggests that the SNPS stock is currently overvalued by 20-25% and conservative long-term investors should be wary of buying at current levels . They should wait for a share price closer to a forward PE of 23-27 times.

Nevertheless, SNPS is an interesting company to have on our watchlist and to follow in the long term.

Annexe 1 : Senior Management Profiles

Chairman and CEO

Aart de Geus is a pioneer in the field of electronic design automation (EDA). His contributions have revolutionized the way digital design is done today.

In the mid-1980s, Dr. de Geus led a team that developed the SOCRATES program, which incorporated timing optimization into a synthesis solution. The R&D at the research center was the genesis for the first broad commercial application of synthesis to modern integrated circuit(IC) design. Synthesis is an essential competitive technology that has changed the way in which IC design is approached.

In 1986 Dr. de Geus founded Synopsys Inc., a global leader in semiconductor design software, intellectual property (IP), design for manufacturing (DFM) solutions and professional services. Currently, he serves as chairman and CEO for Synopsys. In the 20 years since the company was founded, Dr. de Geus has helped Synopsys grow from a start-up, to a software company with annual sales in excess of $1 billion.

An IEEE Fellow, Dr. de Geus has authored more than 25 papers on logic synthesis, simulation, timing, and interconnect delay. He holds a masters of science in electrical engineering from Swiss Federal Polytechnical Institute, Switzerland and a doctorate in electrical engineering from Southern Methodist University, TX. Dr. de Geus was named CEO of the year in 2002 by Electronic Business magazine, 2004 Entrepreneur of the Year in IT for California by Ernst & Young and one of the 10 Most Influential Executives of 2005 by Electronic Business magazine

President and Chief Operating Officer

Sassine Ghazi leads and drives strategy for all business units, sales and customer success, strategic alliances, marketing and communications at Synopsys. He joined the company in 1998 as an applications engineer. He then held a series of sales positions with increasing responsibility, culminating in leadership of worldwide strategic accounts. He was then appointed general manager for all digital and custom products, the largest business group in Synopsys.

Under his leadership several innovative solutions were launched, including the flagship Fusion Design Platform™ which includes 3DIC Compiler, DSO.ai™ and the SiliconMAX™ Silicon Lifecycle Management Platform. He assumed the role of chief operating officer in August, 2020 and was appointed to the role of president in November 2021. Prior to Synopsys he was a design engineer at Intel.

Sassine brings multiple decades of chip design, applications engineering, customer support, sales, and business management experience to Synopsys. He has developed deep customer relationships during his years in sales and he has a passion for collaboration and innovation. He holds a bachelor’s degree in Business Administration from Lebanese American University; a B.S.E.E from the Georgia Institute of Technology and an M.S.E.E. from the University of Tennessee.

General Manager - Electronic Design Automation (EDA) Group.

Shankar Krishnamoorthy is the general manager (GM) of the Electronic Design Automation (EDA) Group. He is responsible for the EDA software line of business across design, verification, signoff, test, silicon lifecycle management (SLM), TCAD, and manufacturing domains for digital, analog, and mixed-signal designs.

Prior to becoming the GM of the EDA Group, Shankar held other executive positions at Synopsys, including GM of the Silicon Realization Group and Digital Design Group and senior vice president of the Digital Implementation Group. Under his leadership, Synopsys has delivered several ground-breaking technologies enabling semiconductor designers to achieve the most optimum power, performance, area, cost and time-to-market on their most advanced products. Before rejoining Synopsys in 2017, Shankar served as GM of the IC Design Solutions Division at Mentor Graphics. He joined Mentor in 2007 with the acquisition of Sierra Design Automation, where he was founder and CTO. Prior to Sierra Design, Shankar led Synopsys’ physical synthesis and logic synthesis R&D organizations.

Shankar received his M.S. in Computer Science from the University of Texas, Austin and his bachelor’s degree in Computer Science from the Indian Institute of Technology, Bombay.

Annexe 2: Synopsys in India

The company has a strong presence in India, with offices in Bangalore, Hyderabad, Noida, Mumbai, and New Delhi. Synopsys India has more than 2,300 employees (10% of the global total) who are involved in the research, design, and development of key technologies and products that enable Smart, Secure Everything in the global electronics market.

Synopsys India's operations include:

R&D : Synopsys India has a strong research and development (R&D) team that is focused on developing new technologies and products that meet the needs of the global electronics market. The team is also involved in the development of new standards for EDA and semiconductor IP.

Sales and marketing: Synopsys India has a dedicated sales and marketing team that is responsible for selling Synopsys' products and services to customers in India and the Asia Pacific region. The team also provides technical support to customers and partners.

Customer support: Synopsys India has a team of experienced engineers who provide technical support to customers and partners. The team is available 24/7 to help customers with their EDA and semiconductor IP needs.

University programs: Synopsys India has a number of university programs that are designed to help students learn about EDA and semiconductor IP. The programs include student internships, training programs, and educational grants.